# Understanding, Modeling, and Improving Main-Memory Database Performance

Stefan Manegold

**About the cover:** The image depicts a relief on a wall of the *Temple of Horus* at Edfu in Upper Egypt between Aswan and Luxor. This major Ptolemaic temple is dedicated to the falcon god *Horus* and was built over a 180-year period from 237 BC to 57 BC. I took the picture during a memorable two-week sightseeing tour through Egypt in September 2000, after having attended the VLDB Conference in Cairo.

# Understanding, Modeling, and Improving Main-Memory Database Performance

ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam, op gezag van de Rector Magnificus prof. mr. P. F. van der Heijden ten overstaan van een door het college voor promoties ingestelde commissie, in het openbaar te verdedigen in de Aula der Universiteit op dinsdag 17 december 2002, te 11.00 uur

door

Stefan Manegold geboren te Eschwege, Duitsland

#### Promotiecommissie

| Promotor:      | M. L. Kersten      |

|----------------|--------------------|

| Overige leden: | D. J. DeWitt       |

|                | P. van Emde Boas   |

|                | L. O. Hertzberger  |

|                | A. P. J. M. Siebes |

|                | G. Weikum          |

### Faculteit

Faculteit der Natuurwetenschappen, Wiskunde en Informatica Universiteit van Amsterdam

The research reported in this thesis has been partially carried out at *CWI*, the Dutch National Research Laboratory for Mathematics and Computer Science, within the theme *Data Mining and Knowledge Discovery*, a subdivision of the research cluster *Information Systems*.

SIKS Dissertation Series No 2002-17. The research reported in this thesis has been carried out under the auspices of *SIKS*, the Dutch Research School for Information and Knowledge Systems.

ISBN 90 6196 517 9

# Contents

|                | Ack  | nowledge  | ements                                              | 9  |

|----------------|------|-----------|-----------------------------------------------------|----|

| 1 Introduction |      |           | 11                                                  |    |

|                | 1.1  | Query P   | rocessing                                           | 12 |

|                | 1.2  |           | odels                                               | 14 |

|                | 1.3  | Increasi  | ng Importance of Memory Access Costs                | 16 |

|                | 1.4  | Research  | h Objectives                                        | 16 |

|                | 1.5  | Thesis C  | Dutline                                             | 18 |

| 2              | Prel | iminaries | 5                                                   | 21 |

|                | 2.1  | Cost Mo   | odels                                               | 21 |

|                |      |           | Cost Components                                     | 21 |

|                |      |           | Cost Factors                                        | 23 |

|                |      | 2.1.3     | Types of (Cost) Models                              | 25 |

|                |      |           | Architecture and Evaluation of Database Cost Models | 26 |

|                | 2.2  | Logical   | Cost Models / Estimation                            | 27 |

|                |      | 2.2.1     | Sampling-based Techniques                           | 28 |

|                |      |           | Parametric Techniques                               | 28 |

|                |      | 2.2.3     | Probabilistic Counting Techniques                   | 29 |

|                |      | 2.2.4     | Non-parametric (Histogram-based) Techniques         | 29 |

|                | 2.3  | I/O-base  | ed Cost Models                                      | 30 |

|                | 2.4  |           |                                                     | 31 |

|                |      | 2.4.1     | Office-By-Example (OBE)                             | 31 |

|                |      | 2.4.2     | Smallbase                                           | 32 |

|                |      | 2.4.3     | Remarks                                             | 34 |

|                | 2.5  | Cost Mo   | odels for Federated and Multi-Database Systems      | 34 |

|                |      | 2.5.1     | Calibration                                         | 34 |

|                |      | 2.5.2     | Sampling                                            | 35 |

|                |      | 2.5.3     | Cost Vector Database                                | 35 |

|                | 2.6  | Main M    | emory Database Systems                              | 36 |

|                | 2.7  | Monet     |                                                     | 37 |

|                |      |           | Design                                              | 37 |

|                |      | 2.7.2     | Architecture and Implementation                     | 39 |

|   |      | 2.7.3    | Query Optimization 40                            |  |

|---|------|----------|--------------------------------------------------|--|

| 3 | Cost | Factor   | s in MMDBMS 41                                   |  |

|   | 3.1  | Comm     | odity Computer Architecture                      |  |

|   |      | 3.1.1    | CPUs 41                                          |  |

|   |      | 3.1.2    | Main-Memory- & Cache-Systems                     |  |

|   | 3.2  | The No   | ew Bottleneck: Memory Access                     |  |

|   |      | 3.2.1    | Initial Example                                  |  |

|   |      | 3.2.2    | General Observations                             |  |

|   |      | 3.2.3    | Detailed Analysis                                |  |

|   |      | 3.2.4    | Discussion                                       |  |

|   |      | 3.2.5    | Implications for Data Structures                 |  |

|   | 3.3  | The Ca   | alibrator: Quantification of Memory Access Costs |  |

|   |      | 3.3.1    | Calibrating the (Cache-) Memory System           |  |

|   |      | 3.3.2    | Calibrating the TLB                              |  |

|   |      | 3.3.3    | Summary                                          |  |

|   | 3.4  |          | r Observations                                   |  |

|   |      | 3.4.1    | Parallel Memory Access                           |  |

|   |      | 3.4.2    | Prefetched Memory Access                         |  |

|   |      | 3.4.3    | Future Hardware Features   69                    |  |

|   |      |          |                                                  |  |

| 4 | Gen  | eric Dat | tabase Cost Models 71                            |  |

|   | 4.1  | Relate   | d Work and Historical Development                |  |

|   | 4.2  | Outline  | e                                                |  |

|   | 4.3  | The Id   | ea                                               |  |

|   |      | 4.3.1    | Data Regions                                     |  |

|   |      | 4.3.2    | Basic Access Patterns                            |  |

|   |      | 4.3.3    | Compound Access Patterns                         |  |

|   | 4.4  | Derivi   | ng Cost Functions                                |  |

|   |      | 4.4.1    | Preliminaries                                    |  |

|   |      | 4.4.2    | Single Sequential Traversal                      |  |

|   |      | 4.4.3    | Single Random Traversal                          |  |

|   |      | 4.4.4    | Discussion                                       |  |

|   |      | 4.4.5    | Repetitive Traversals                            |  |

|   |      | 4.4.6    | Random Access                                    |  |

|   |      | 4.4.7    | Interleaved Multi-Cursor Access                  |  |

|   | 4.5  | Combi    | ning Cost Functions                              |  |

|   |      |          | Sequential Execution                             |  |

|   |      | 4.5.2    | Concurrent Execution                             |  |

|   |      | 4.5.3    | Query Execution Plans                            |  |

|   | 4.6  |          | Costs                                            |  |

|   |      | 4.6.1    | What to calibrate?                               |  |

|   |      | 4.6.2    | How to calibrate?                                |  |

|   |      | 4.6.3    | When to calibrate?                               |  |

|   | 4.7  |          | mental Validation                                |  |

|   |      | r        |                                                  |  |

6

|   |                     | 4.7.1    | Setup                                        | 98  |

|---|---------------------|----------|----------------------------------------------|-----|

|   |                     | 4.7.2    | Results                                      | 98  |

|   | 4.8                 | Conclu   | sion                                         | 103 |

| 5 | Self                |          | Cache-conscious Join Algorithms              | 105 |

|   | 5.1                 | Introdu  | uction                                       | 105 |

|   |                     | 5.1.1    | Related Work                                 | 107 |

|   |                     | 5.1.2    | Outline                                      | 108 |

|   | 5.2                 | Partitic | oned Hash-Join                               | 109 |

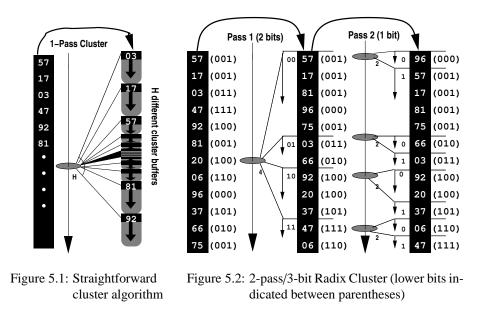

|   |                     | 5.2.1    | Radix-Cluster Algorithm                      | 110 |

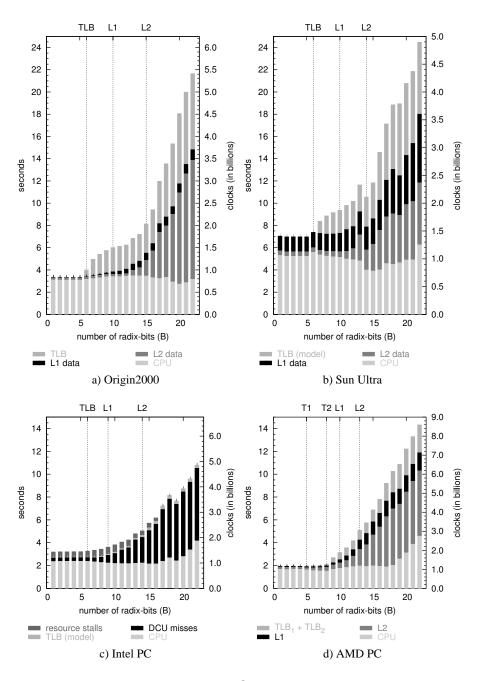

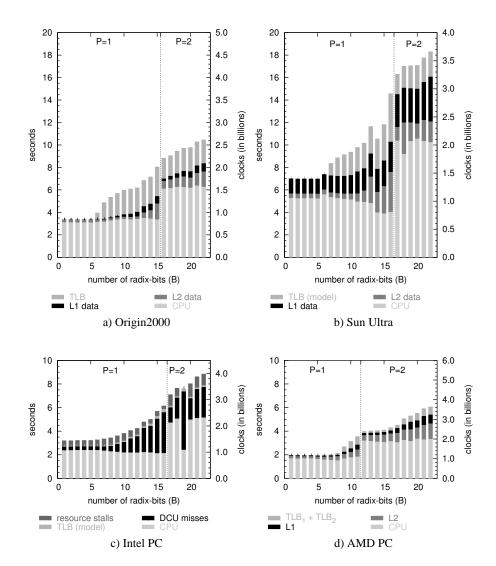

|   |                     | 5.2.2    | Quantitative Assessment                      | 110 |

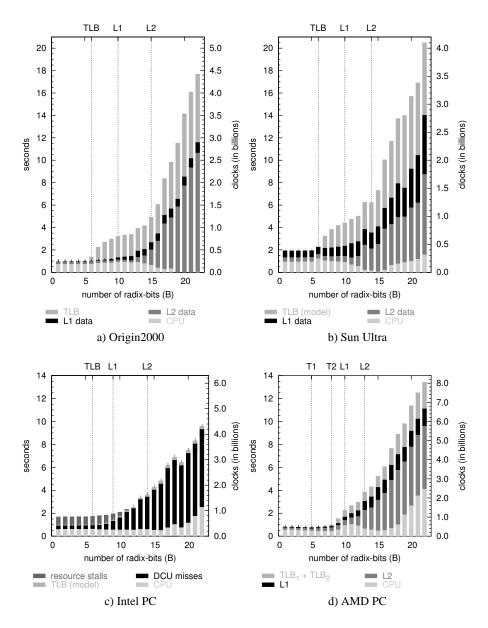

|   | 5.3                 | Radix-   | Join                                         | 131 |

|   |                     | 5.3.1    | Isolated Radix-Join Performance              | 131 |

|   |                     | 5.3.2    | Overall Radix-Join Performance               | 134 |

|   |                     | 5.3.3    | Partitioned Hash-Join vs. Radix-Join         | 134 |

|   | 5.4                 | Evalua   | tion                                         | 134 |

|   |                     | 5.4.1    | Implications for Implementation Techniques   | 136 |

|   |                     | 5.4.2    | Implications for Query Processing Algorithms | 139 |

|   |                     | 5.4.3    | Implications for Disk Resident Systems       | 139 |

|   | 5.5                 | Conclu   | ision                                        | 140 |

| 6 | Sum                 | imary a  | nd Outlook                                   | 141 |

|   | 6.1                 | Contril  | butions                                      | 141 |

|   | 6.2                 | Conclu   | lsion                                        | 143 |

|   | 6.3                 | Open I   | Problems and Future Work                     | 143 |

|   | Bibl                | iograph  | y                                            | 145 |

|   | Curriculum Vitae 16 |          |                                              | 161 |

|   |                     | Publica  | ations                                       | 162 |

|   | List                | of Tabl  | es and Figures                               | 165 |

|   | List                | of Sym   | bols                                         | 167 |

|   | Samenvatting        |          | 171                                          |     |

8\_\_\_\_\_

# Acknowledgements

My first visit to Amsterdam during an InterRail-tour through Europe in summer 1992 lasted only a few hours and left an impression of anything else but hospitality: All left-luggage lockers occupied, endless queues in front of the left-luggage office, and sightseeing while carry a heavy backpack was not much fun. It took another 5 years, a move from C. where I had studied to B. where I got my first (real) job, two much more pleasant visits in summer 1997, during which A. presented itself in an almost Mediterranean atmosphere, and finally a job offer, to convince me that Amsterdam might be a place to life and work. However, with the contract signed and everything else arranged, there was no need anymore for a Mediterranean atmosphere, hence, when I arrived on October 1st 1997 it started raining and did not stop until March 1998... Nevertheless, I did stay, enjoyed life and work in Amsterdam, and eventually wrote this booklet.

Although only one name appears on the cover, this thesis would not exist without the direct or indirect support of various helpful people who accompanied me during the last five years, both locally and remotely. I take this opportunity to express my thanks to all of them.

First of all, I would like to thank my supervisor Martin Kersten. Together with Arno Siebes, he provided me with this great opportunity to come to Amsterdam and do research in an inspiring and well-funded group. Back then, both of us had no idea, which "problems" would pop-up a few years later. The more I am grateful to him for convincing me, whenever I lost faith, that all the struggling will eventually lead to a successful and (hopefully) happy end.

Further, I would like to thank David DeWitt, Peter van Emde Boas, Louis Hertzberger, Arno Siebes, and Gerhard Weikum for being on my committee. It is a great honor for me, that all of them found time to read my theses.

Special thanks go to all my Dutch and international colleagues within INS for the warm welcome they gave me right from the beginning, and their support after my most memorable encounter with Amsterdam traffic. Some of them shall be mentioned here, but I am thankful to all the others as well.

Two colleagues at CWI played major roles during my PhD track. Working together with Florian and Peter, and writing successful papers with both of them (though not at the same time) has been a privilege, an enlightning experience, and a great pleasure that I would not want to miss. Long deadline-nights with last-minute-submission adrenaline were always rewarded by "traditional dinners", at least as long nights with "contemporary music" or Pauwel Kwak and his friends, and finally joint conference trips. I hope there is more to come in the future.

Work at CWI would not have been that interesting, if there had not been "some" distractions from the pure research work. I could not imagine a better colleague for system administration and "Monet-hacking" than Niels. We do speak the same language, not only when talking about "common enemies". Menzo has been the perfect room mate. Not only did he accept my irregular office hours, but he also showed great patience and helpfulness with all my nasty questions and problems, ranging from Dutch language and culture over details of Monet to various computer- and software-related problems. Always walking a few steps ahead of me, Albrecht guided my way through all the administrative and technical hurdles of the last few month of this project.

Finally, I want thank all my "old friends from home". Despite being spread (almost) all over Europe, we stayed in touch, meat at various parties, spent fortunes on phone bills, and some of them even managed to visit me in Amsterdam. Not loosing contact to them has been vital for my Amsterdam-project. I am especially grateful to my most frequent (and most welcome) visitor that she has been concerned of and took care of my cultural life.

Insbesondere danke ich auch meiner Familie. Ohne Eure Geduld und Eure Unterstützung — nicht nur was mein leibliches Wohl angeht ;-) — wäre diese Arbeit nicht möglich gewesen.

Amsterdam, November 2002

# Chapter 1

# Introduction

Databases have not only become essential to business and science, but also begin to appear more and more in everyday life. Classically, databases are used to maintain internal business data about employees, clients, accounting, stock, and manufacturing processes. Furthermore, companies nowadays use them to present data to customers and clients on the World-Wide-Web. In science, databases store the data gathered by astronomers, by investigators of the human genome, and by biochemists exploring the medical properties of proteins, to name only a few examples. With home-PC's becoming more and more powerful — one can easily get 1 gigabyte (*GB*) of mainmemory and up to 160 GB on a single commodity disk drive — database systems are beginning to appear as a common tool for various computer applications, much as spreadsheets and word processors did before them. Even in portable devices, such as PDAs or mobile phones, (small) databases are used for storing everything from contact information such as postal addresses and phone numbers to your digital family photo album. And smart-cards storing a persons medical history are just around the corner.

The power of databases comes from a body of knowledge and technology that has developed over several decades and is embodied in specialized software called a *database management system*, or *DBMS*, or colloquially a "database system". DBMSs are among the most complex types of software available. A DBMS is a powerful tool for creating and managing large amounts of data efficiently. First of all, it provides capabilities allowing safe and persistent storage of data over long periods of time. Furthermore, DBMSs provide powerful query<sup>1</sup> languages, such as for instance *SQL* (*Structured Query Language*), that allow both interactive users and application programs to access and modify the data stored in the database.

In this thesis, we assume the reader is familiar with the basic concepts of DBMSs and database query processing as described in good introductory literature, for instance [KS91, EN94, AHV95, GMUW02].

<sup>&</sup>lt;sup>1</sup>A "query" is database lingo for a question about the data.

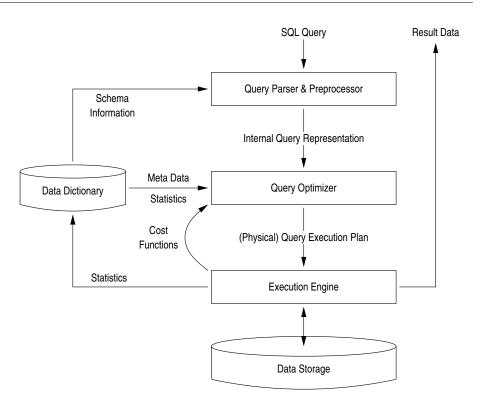

Figure 1.1: Query Processing Architecture

## **1.1 Query Processing**

A major reason why database systems have become so popular and successful is the fact that users can formulate their queries in an almost "intuitive" way using declarative query languages such as SQL. This means, that users just have to care about *what* they want to know, but not *how* to retrieve this information from the data stored in the database. In particular, users do not need to have any sophisticated programming skills or knowledge about how the DBMS physically stores the data. All a user needs to know to formulate ad-hoc queries is the query language and the logical database schema.

Completely hidden from the user, a complex machinery within the DBMS then takes care of interpreting the user's query and executing the right commands to provide the user with the requested answer. Figure 1.1 roughly sketches a typical database system's query processing architecture.<sup>2</sup>

Briefly, query processing consists of the following steps. First, the query text is

<sup>&</sup>lt;sup>2</sup>The complete architecture of nowadays DBMSs is obviously much more complex. Here, we focus on the parts that are related to the work in this thesis. We also omit details that are not specific to problems and techniques addressed in this work.

parsed, checked for syntactical and semantical correctness, and translated into an internal representation. In relational DBMSs, this representation is typically derived from the *relational algebra* and makes up some kind of *operator tree*. Due to certain properties of the relational algebra, such as commutativity and associativity of operators, each query can be represented by various operator trees. These trees are obviously equivalent in that they define the same query result. However, the order in which the various operators are applied may differ. Moreover, relational algebra provides equivalent alternatives for certain operator combinations. One of the most prominent examples is the following. Imagine a sequence where a cartesian product of two tables, say  $\times(U, V)$ , is followed by a selection  $\sigma$  applying a predicate  $\theta$  on the newly combined table:  $\sigma_{\theta}(\times(U, V))$ . This sequence can alternatively be expressed as a single join operation  $\bowtie$  on the two tables, i.e.,  $\sigma_{\theta}(\times(U, V)) \equiv \bowtie_{\theta} (U, V)$ . Usually, database query processors apply some normalizations first, to provide a "clean" starting point for the subsequent tasks.

In a second step, the normalized operator tree has to be translated into a procedural program that the DBMS's query engine can execute. We call such a program a query execution plan (QEP), or simply query plan. Usually, a declarative query can be translated into several equivalent QEPs. These QEPs may differ not only in the order of operator execution (see above), but also in the algorithms used for each single operator (e.g., hash-join, merge-join, and nested-loop-join are the most prominent join algorithms), and in the kind of access structures (such as indices) that are used. The DBMS's query optimizer is in charge of choosing the "best" (or at least a "reasonably good") alternative. The goal or objective (function) of this optimization depends on the application. Traditional goals are, e.g., to minimize the response time (for the first answer, or for the complete result), to minimize the resource consumption (like CPU time, network bandwidth or amount of memory), or to maximize the throughput, i.e., the number of queries that the system can answer per time. Other, less obvious objectives - e.g., in a mobile environment - may be to minimize the power consumption needed to answer the query or the on-line time being connected to a remote database server.

For the time being, we do not have to distinguish between these different objective functions. Hence, we use the common terminology in the database world, and call them the *execution costs* or simply *costs* of the QEP. Thus, query optimization means to find a QEP with minimal execution costs.

Conceptually, query optimization is often split into two phases. First, the optimizer determines the order in which the single operators are to be applied. This phase is commonly referred to as *logical optimization*. By definition, the final result size is the same for all equivalent QEPs of a given query. However, with different operator orders, the intermediate result sizes may vary significantly. Assuming that the execution costs of each operator, and hence of the whole QEP, are mainly determined by the amount of data that is to be processed, logical optimization usually aims at minimizing the total sum of all intermediate result sizes in a QEP. In a second phase, commonly called *physical optimization*, the query optimizer determines for each operator in the QEP, which of the available algorithms is to be used and whether existing access structures (e.g., indices) can/should be exploited. Physical optimization aims at actually minimizing the execution costs with respect to the given cost metric.

In practice, however, the implicit assumption that the best *physical plan* can be derived from the best *logical plan* usually does not hold. Hence, query optimization is often performed in a single phase combining both logical and physical optimization. A further discussion of this subject, especially the problems that arise due to the increased complexity of the optimization process, is beyond the scope of the thesis. The interested reader is referred to, e.g., [Cha98, Pel97, Waa00]. In this work, we focus on cost modeling and consider cost models independently from a particular optimization algorithm.

## 1.2 Cost Models

In order to find the desired QEP, optimizers need to assess and compare different alternatives with respect to their costs. Obviously, evaluating a QEP to measure its execution cost does not make sense. Hence, we need to find a way to *predict* the execution costs of a QEP *a priori*, i.e., without actually evaluating it.

This is where *cost models* come into play. Cost models can be seen as abstract images or descriptions of the real system. Providing a simplified view of the system, (cost) models help us to analyze and/or better understand how a system works, and hence, enable us to estimate query execution costs within this "idealized" abstract system without actually executing the query. The abstraction from the real system is captured in a set of assumptions made about the system, e.g., assuming uniform data distributions, independence of attribute values, constant cost (time) per I/O operation, no system contention, etc.. The degree of abstraction depends on the purpose the cost model is supposed to serve. In general, the more general assumptions are made, i.e., the more abstract the model is, the less adequate or accurate it is. The more detailed a model is, the more accurate it is. The most detailed, and hence most accurate, model is the system itself. However, not only the accuracy of a model is important, but also the time necessary to derive estimations using the model. Here, it usually holds, that evaluation time decreases with the increasing degree of abstraction. In other words, the less accurate a model is, the faster can estimations be evaluated. For instance, models based on *simulation* provide a very detailed image of the real system, and hence allow very accurate estimates. Evaluating the model, however, means running a simulation experiment, which might take even longer than running the real system. On the other hand, using more general assumptions makes the models simpler. Simple models might then be represented in closed mathematical terms. We call these models analytical models. Evaluating analytical models means simply evaluating (a set of) closed mathematical expressions. This is usually much faster than both evaluating simulation models and evaluating the real system. This trade-off between accuracy and evaluation performance is one of the most important factors to be considered when choosing or designing models for certain purposes.

In principle, query optimization does not require very accurate cost models that estimate the execution cost to the microsecond. The major requirement here is, that the costs estimated by the cost model generate the same order on the QEPs as the actual execution costs do. The "cheapest" of a set of candidate QEPs is still the very same QEP, even if the cost model is off by an order of magnitude for all plans (provided it is off in the same direction for all plans). We use the term *adequate* for such cost models that preserve the order among the QEPs but are not necessarily accurate. As the query optimization problem is in general NP-hard [IK84, CM95, SM97], finding *the best* plan is practically not possible in reasonable time. Hence, optimization strategies usually (try to) find *a reasonably good* plan.<sup>3</sup> This in turn means that is it not necessary to preserve the proper order of plans whose costs are "very similar"; actually, it is often not even necessary to distinguish plans with very similar costs at all.

Many traditional disk-based DBMSs make use of these properties. In a disk-based DBMS, access to secondary storage is the dominating cost factor. To keep cost models simple, they often neglect other cost factors and estimate only I/O costs. Sometimes, I/O costs are not even given in time needed to perform the required I/O operations, but simply the number of necessary I/O operations is estimated.

However, there are situations where these simplifications do not apply as more accurate costs are required. For instance, two plans may differ in a way that one requires more I/O operations while the other one requires more computation time. To compare such plans, we need to express their total costs (i.e., I/O + CPU) in a common unit (i.e., time). Also the objective function or the stopping criterion for the optimization process might require more accurate costs in terms of processing time: "Stop optimization when the cheapest plan found so far takes less than 1 second", or "Stop optimization when the total time spent on optimization has reached a certain fraction of the execution time of the cheapest plan found so far".

In this thesis, we consider the following three cost components. A more elaborate description is given in Chapter 2.

- **Logical Costs** consider only the data distributions and the semantics of relational algebra operations to estimate intermediate result sizes of a given (logical) query plan.

- Algorithmic Costs extend logical costs by taking also the computational complexity (expressed in terms of *O*-classes) of the algorithms into account.

- **Physical Costs** finally combine algorithmic costs with system/hardware specific parameters to predict the total costs in terms of execution time.

Next to query optimization, cost models can serve another purpose. Especially algorithmic and physical cost models can help database developers to understand and/or predict the performance of existing algorithms on new hardware systems. Thus, they can improve the algorithms or even design new ones without having to run time and resource consuming experiments to evaluate their performance.

<sup>&</sup>lt;sup>3</sup>A further discussion of optimization strategies is beyond the scope of this thesis.

# 1.3 Increasing Importance of Memory Access Costs

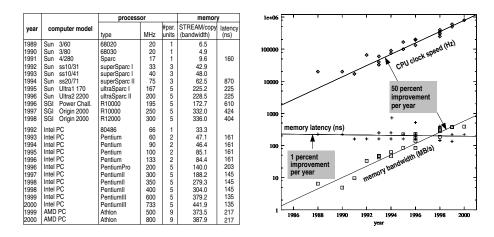

Looking at the hardware development over, the last two decades, we recognized two major trends. On the one hand, CPU speed keeps on following Moore's law [Moo65], i.e., it doubles about every 18 months. In other words, clock speeds increase by more than 50 percent per year, and there are no indications that this trend might significantly change in the foreseeable future. Concerning main-memory, the picture looks differently. While main-memory sizes and main-memory bandwidth almost keep up with the CPU development, main-memory access latency is increasingly staying behind, improving only about 1 percent per year. New DRAM standards like Rambus and SLDRAM continue concentrating on improving the bandwidth, but hardly manage to reduce the latency. Hence, the performance gap between CPU speed and memory latency that has grown significantly over the last two decades is expected to widen even more in the near future.

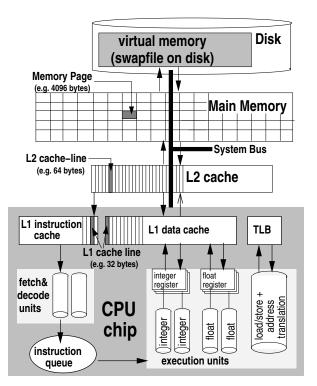

To bridge the gap, hardware vendors have introduced small but fast cache memories — consisting of fast but expensive SRAM chips — between the CPU and mainmemory. Nowadays, cache memories are often organized in two or three cascading levels, with both their size and latency growing with the distance from the CPU. Cache memories can reduce the memory latency, only if the requested data is found in one of the cache levels. This mainly depends on the application's memory access pattern. Hence, it becomes the responsibility of software developers to design and implement algorithms that make optimal use of the very cache/memory architecture the respective application runs on.

Standard main-memory database technology has mainly ignored this hardware development. The design of algorithms and especially cost models is still based on the assumptions that did hold in the early 80's. Without I/O as dominant cost factor, costs are commonly reduced to CPU processing costs. Memory access, if not considered negligible compared to CPU costs, is assumed to be uniform.

With memory sizes in commodity hardware getting larger at a rapid rate, also in disk-based DBMSs many database processing tasks can more and more take place in main memory.<sup>4</sup> As the persistent data remains located on disk farms, initial data access still requires disk I/O. But once the query operands are identified and streamed into memory, large intermediate results, temporary data structures, and search accelerators will fit into main memory, significantly reducing the number of I/O operations. With powerful RAID systems and high-capacity I/O buses reducing the I/O bandwidth at a rate that roughly matches the improvements in CPU speed, even in disk-based DBMSs memory access is expected to become a cost factor that can no longer be ignored.

## **1.4 Research Objectives**

Concerning cost modeling, both data volume estimations and complexity measures are independent of the underlying system and hardware architecture. However, the per-

<sup>&</sup>lt;sup>4</sup>"... the typical computing engine may have one terabyte of main memory. "Hot" tables and most indexes will be main-memory resident." [BBC<sup>+</sup>98].

formance experienced in terms of time costs is heavily dependent on these parameters. In this thesis, we devote ourselves to the latter, also referred to as physical costs. The research in this thesis is driven by three major questions:

Understanding: What is the impact of the increasing gap between CPU and memory

access costs on main-memory database performance?

- **Modeling:** Is it possible to predict memory access cost accurately, and if so, how should the respective physical cost functions be designed?

- **Improving:** What can we learn from analyzing and modeling main-memory database performance on hierarchical memory systems, and how can we use this knowledge to improve main-memory database technology?

In more detail, the research problems and objectives addressed in this document are formulated as follows:

**Understanding** Predicting physical query processing costs requires in-depth insight in how database software and modern hardware do interact. Hence, the first problem is to identify which hardware-specific parameters determine the processing costs in a main-memory database, and therefore need to be reflected in the cost models. It is desirable to analyze various hardware platforms to identify the commonalities and differences of the performance characteristics.

**Modeling** Another open issue is how to acquire new cost models. Traditionally, physical cost functions highly depend on various parameters that are specific to the very DBMS's software (e.g., the algorithms used and the way they are implemented) and to the hardware the database systems is running on (such as disk access latencies, I/O bandwidth, memory access speed, CPU speed, etc.). Thus, physical cost functions are usually created "by hand" for each algorithm, each DBMS, and each platform individually. This approach is not only time-consuming, but also tends to be error-prone. Hence, the question is whether — and if so, how — the process of designing physical cost models can be simplified and/or automated. Moreover, the generic use of database software on a range of platforms requires an analysis of their portability. The problem is, that we need to find a proper set of parameters describing the hardware-specific features and to design a cost model that can use these parameters.

**Improving** The main task of performance modeling is to understand and describe the behavior of a given system consisting of certain hardware and software components. However, while analyzing the details, one often is confronted with a priori unknown bottlenecks that might have to be minimized or even eliminated to improve the performance. The final question addressed in this thesis is whether and how we can use both the cost models we created and the knowledge gained while developing them, to improve main-memory database technology.

# 1.5 Thesis Outline

The research objectives mentioned above are explored in detail in the remaining chapters.

In Chapter 2, we dedicate ourselves to preliminaries, briefly reviewing the role of performance models in database literature. We mainly focus on the different types of cost models, the various purposes they serve, and proposed techniques how to acquire cost models for a given system and purpose. Moreover, we give a concise overview of our main-memory DBMS prototype Monet, which we use as implementation and validation platform throughout this thesis.

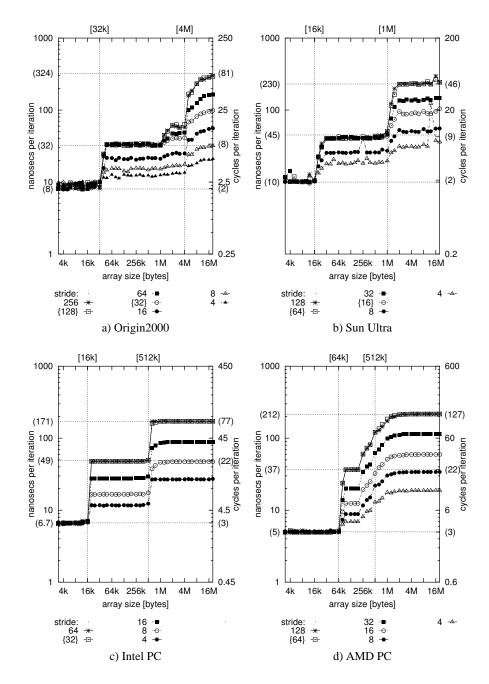

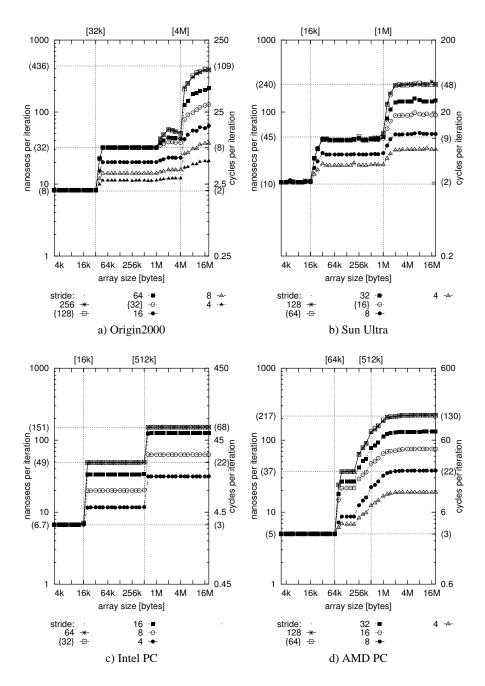

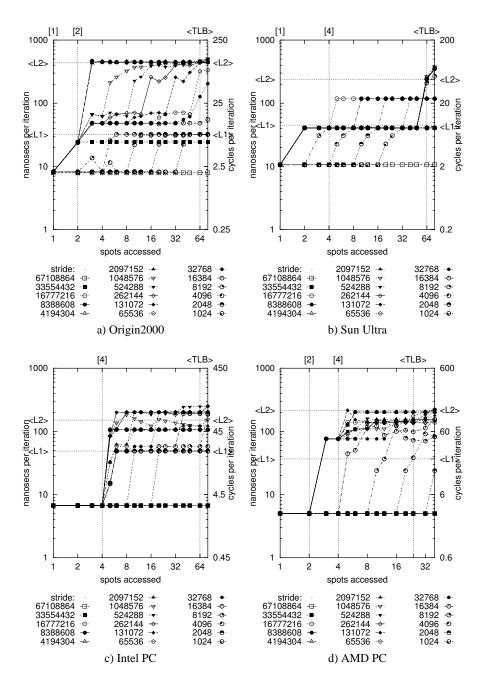

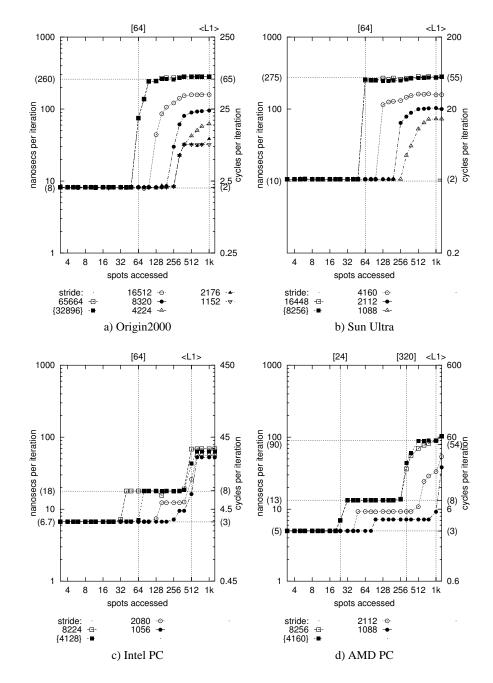

In order to create database cost models, we need to know which parameters are relevant for the performance behavior of database algorithms. In Chapter 3, we first discuss the characteristics of state-of-the-art CPU, cache-, and main-memory architectures. Our research covers various hardware platforms, ranging form standard PC's over workstations to high-performance servers. For convenience, we introduce a unified hardware model, that gathers the performance-relevant characteristics of hierarchical memory systems — including CPU caches, main-memory, and disk systems in a single framework. The unified hardware model provides the necessary abstraction to treat various hardware platforms equally on a qualitative level. Equipped with these technical details, we analyze the impact of various hardware characteristics on the performance of database algorithms. In particular, we show that on modern hierarchical memory systems (consisting of the main memory and one or more levels of caches) memory access must not be seen as "for free", not even as uniform, concerning costs. Hence, traditional cost models focusing on I/O and CPU costs are not suitable any more. To adequately predict database performance in the new scenario, where main memory access is (partly) replacing the formerly cost-dominating disk access, new cost models are required that respect the performance impact of hierarchical memory systems. The analysis results in a calibration tool that automatically derives the relevant hardware characteristics, such as cache sizes, cache miss latencies, and memory access bandwidths, from any hardware platform. The ability to quantify these hardware features lays the foundation for hardware independent database cost models.

Equipped with the necessary tools, we are ready to design hardware independent physical database cost models in Chapter 4. Focusing on data access costs, we develop a cost model that achieves hardware independence by using the hardware characteristics as parameters. The unified hardware model permits the creation of parameterized cost functions. Porting these functions to other systems or hardware platforms can then simply be done by filling in the new specific parameters as derived by our calibration tool. Moreover, we propose a generic approach that simplifies the task of creating cost functions for a plethora of database operations. For this purpose, we introduce the concept of data access patterns as a method to describe the data access behavior of database algorithms in an abstract manner. Based on this concept, we propose a novel generic technique to design cost models.

In Chapter 5, we demonstrate how to use the knowledge gained during our work on database performance modeling to design algorithms that efficiently exploit the performance potentials of contemporary hardware architectures.<sup>5</sup> Focusing on join algorithms in a main-memory scenario and pursuing our line of generic and portable solutions, we propose new cache-conscious algorithms that automatically adapt to new hardware platforms. In this context, our cost models serve a triple purpose. First, they prove valuable to model and hence understand the performance behavior of different algorithms in various hardware environments. Second, they enable us to design algorithms that can be tuned to achieve the best performance on various hardware platform. Tuning is done automatically at runtime, using the cost models and the parameters as measured by our calibration tool. And third, of course, our cost functions serve as input for cost-based query optimization.

The thesis is concluded in Chapter 6, which summarizes the contributions and discusses future research directions.

Much of the material presented in this thesis has been published in preliminary and condensed form in the following papers:

P. A. Boncz, S. Manegold, and M. L. Kersten. Database Architecture Optimized for the New Bottleneck: Memory Access. In *Proceedings of the International Conference on Very Large Data Bases (VLDB)*, pages 54–65, Edinburgh, Scotland, UK, September 1999.

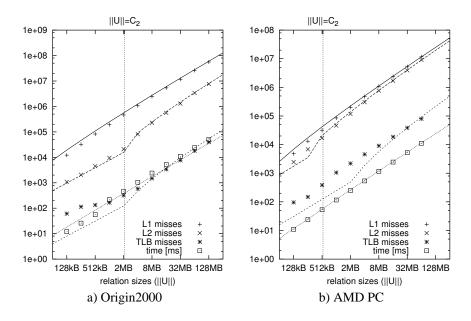

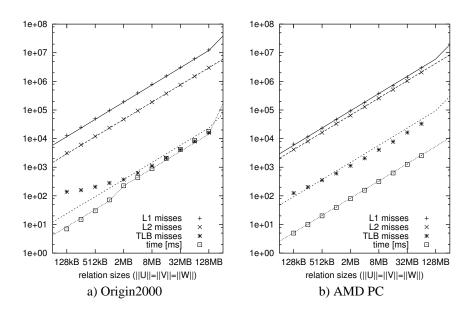

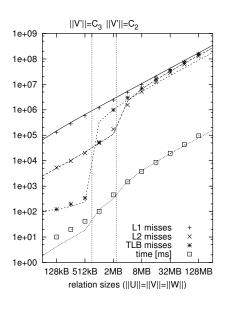

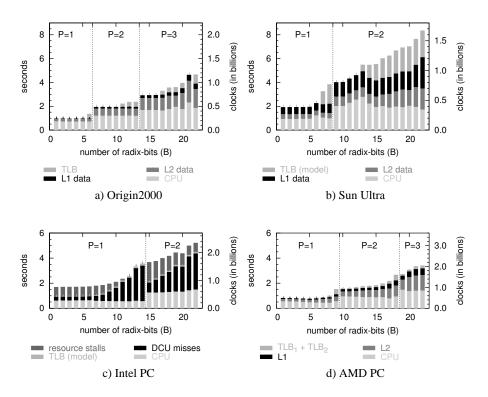

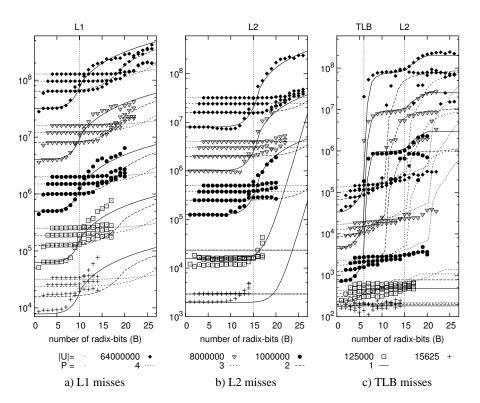

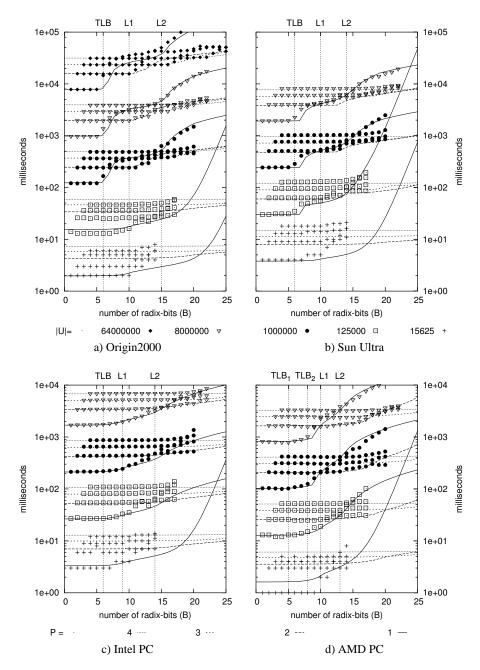

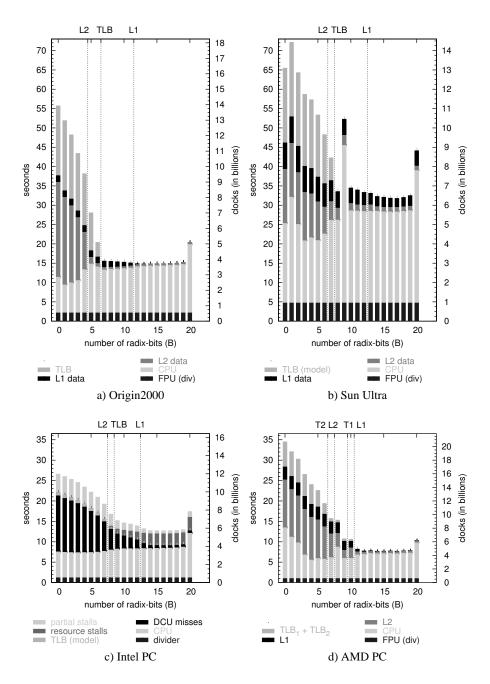

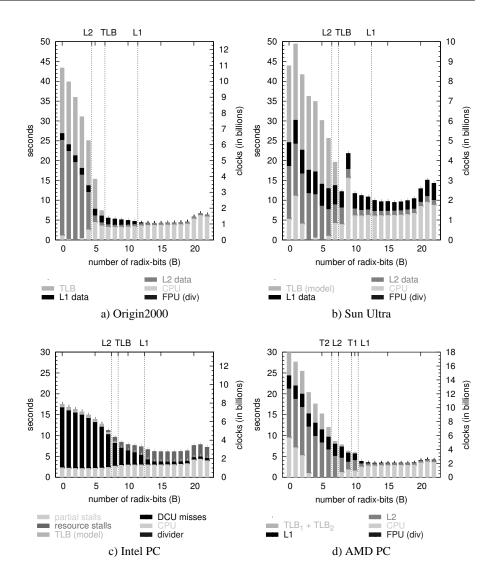

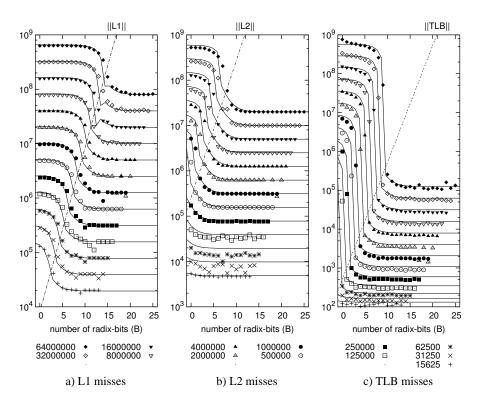

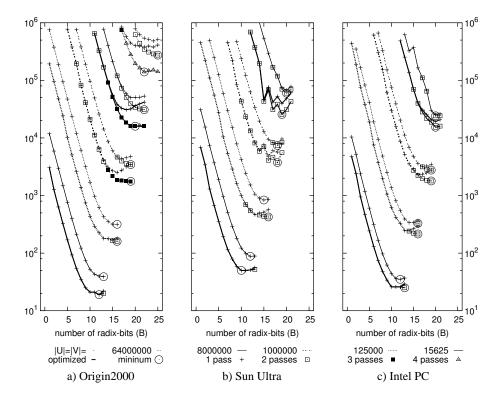

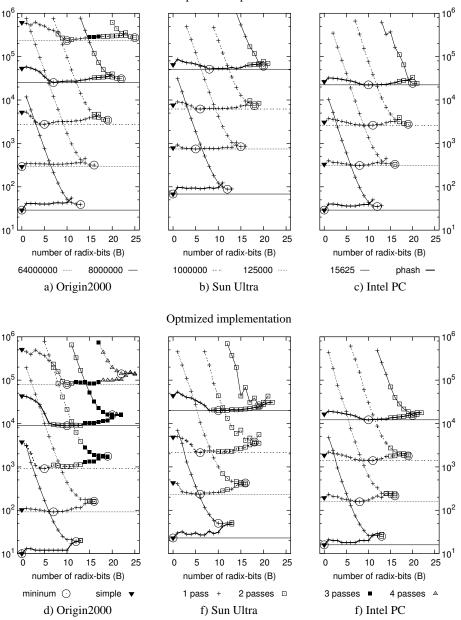

The paper analyzes the impact of modern hardware trends on database query performance. Exhaustive experiments on an SGI Origin2000 demonstrate that main-memory access forms a significant bottleneck with traditional database technology. Detailed analytical performance models are introduced to describe the memory access costs of some join algorithms. The insights gained are translated into guidelines for future database architecture, in terms of both data structures and algorithms. We discuss how vertically fragmented data structures optimize cache performance on sequential data access. Further, we present new radix algorithms for partitioned nested-loop- and hash-join. Detailed experiments confirm that these hardware-conscious algorithms improve the join performance by restricting random data access to the smallest cache size.

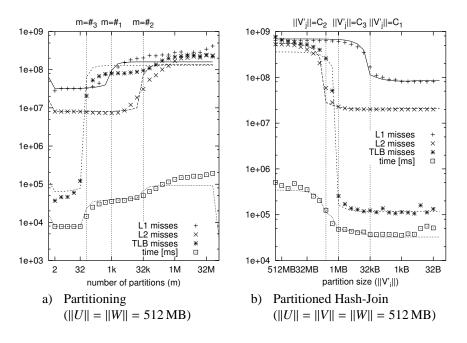

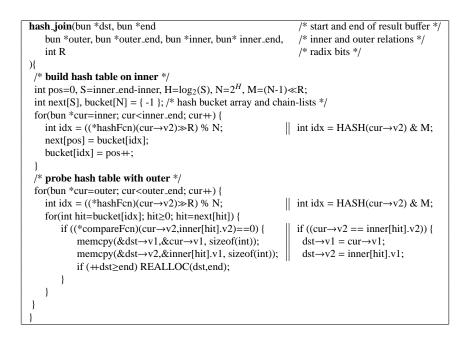

• S. Manegold, P. A. Boncz, and M. L. Kersten. Optimizing Database Architecture for the New Bottleneck: Memory Access. *The VLDB Journal*, 9(3):231–246, December 2000.

This extended version of the previous paper has been re-published in the "Bestof-VLDB 1999" collection. The paper provides a more detailed analysis of main-memory access cost on core database algorithms. Analytical models are presented that also cover the effects that occur due to CPU work and memory access overlapping each other. Moreover, we present a revised version of our partitioned hash-join algorithm. We found out that using perfect hashing instead of aiming at an average hash-bucket size of 4 tuples, improved the performance significantly by reducing the number of cache misses that occur while following the collision list. With this improvement, partitioned hash-join became superior to radix-join, which was faster in our initial experiments.

<sup>&</sup>lt;sup>5</sup>Joint work with Peter Boncz; certain parts do overlap with parts of his Ph.D. thesis [Bon02].

S. Manegold, P. A. Boncz, and M. L. Kersten. What happens during a Join?

Dissecting CPU and Memory Optimization Effects. In *Proceedings of the International Conference on Very Large Data Bases (VLDB)*, pages 339–350, Cairo, Egypt, September 2000.

In this paper, we show that CPU costs become distinctive, once memory access is optimized as proposed in our previous work. Exhaustive experimentation on various hardware platforms indicates that conventional database code is much too complex to be handled efficiently by modern high-performance CPUs. In turns out that especially function calls and branches make the code unpredictable for the CPU and thus hinder efficient use of the CPU internal parallel resources. We propose new coding techniques that enable better exploitation of the available resource. Experiments on various hardware platforms show that optimizing memory access and CPU resource utilization support each other, yielding a total performance improvement of up to an order of magnitude.

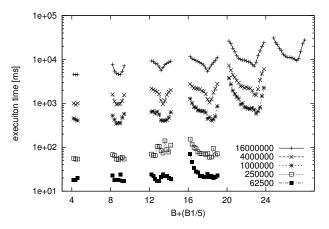

S. Manegold, P. A. Boncz, and M. L. Kersten. Optimizing Main-Memory Join On Modern Hardware. *IEEE Transactions on Knowledge and Data Engineering (TKDE)*, 14(4):709–730, July 2002.

This work discusses our work on analyzing, modeling, and improving memory access and CPU costs in a broader context. We provide refined cost models for our radix-based partitioned hash-join algorithms. Being parameterized by architecture-specific characteristics such as cache sizes and cache miss penalties, our models can be easily ported to various hardware platform. We introduce a calibration tool to automatically measure the respective hardware parameters.

• S. Manegold, P. A. Boncz, and M. L. Kersten. Generic Database Cost Models for Hierarchical Memory Systems. In *Proceedings of the International Conference on Very Large Data Bases (VLDB)*, pages 191–202, Hong Kong, China, August 2002.

In this paper, we present a generalized framework for our cost models. We provide a novel unified hardware model to describe performance relevant characteristics of hierarchical memory systems, hardware caches, main-memory, and secondary storage. Together with our calibration tool, this unified hardware model allows automatic porting of our cost models to various hardware platforms. To simplify the task of designing physical cost functions for various database algorithms, we introduce the concept of data access patterns. The data access behaviors of an algorithm is described in terms of simple combinations of basic patterns such as "sequential access" or "random access". From this description, the detailed physical cost functions are derived automatically using the rules we developed in this work. The resulting cost functions estimate the number of accesses to each level of the memory hierarchy and score them with their respective latency. Respecting the features of both disk drives and modern DRAM-chips, we distinguish different latencies for sequential access.

# Chapter 2

# **Preliminaries**

Models play a very important role in science and research. Usually, a model is seen as an abstract image or description of a certain part of "the real world" that helps us to analyze and/or better understand this part of the real world. As we saw in Chapter 1, database systems rely on cost models to do efficient and effective query optimization. In this chapter, we first discuss some fundamentals of cost models and informally introduce the terminology we use throughout this thesis. Then, we briefly review the role of database cost models in literature and discuss some approaches in more detail. The last part of this chapter gives a concise overview of our main-memory DBMS prototype Monet, which we use as implementation and validation platform throughout this thesis.

# 2.1 Cost Models

We indicated in Chapter 1 that different execution plans require different amounts of effort to be evaluated. The objective function for the query optimization problems assigns every execution plan a single non-negative value. This value is commonly referred to as *costs* in the query optimization business.

## 2.1.1 Cost Components

In the Introduction, we mentioned already briefly that we consider cost models to be made up of three components: logical costs, algorithmic costs, and physical costs. In the following, we discuss these components in more detail.

### 2.1.1.1 Logical Costs / Data Volume

The most important cost component is the amount of data that is to be processed. Per operator, we distinguish three data volumes: input (per operand), output, and temporary data. Data volumes are usually measured as cardinality, i.e., number of tuples. Often, other units such as number of I/O blocks, number of memory pages, or

total size in bytes are required. Provided that the respective tuple sizes, page sizes, and block sizes are known, the cardinality can easily be transformed into the other units.

The amount of input data is given as follows: For the leaf nodes of the query graph, i.e., those operations that directly access base tables stored in the database, the input cardinality is given by the cardinality of the base table(s) accessed. For the remaining (inner) nodes of the query graph, the input cardinality is given by the output cardinality of the predecessor(s) in the query graph.

Estimating the output size of database operations — or more generally, their *selectivity* — is anything else but trivial. For this purpose, DBMSs usually maintain statistic about the data stored in the database. Typical statistics are

- cardinality of each table,

- number of distinct values per column,

- highest / lowest value per column (where applicable).

Logical cost functions use these statistics to estimate output sizes (respectively selectivities) of database operations. The simplest approach is to assume that attribute values are uniformly distributed over the attribute's domain. Obviously, this assumption virtually never holds for "real-life" data, and hence, estimations based on these assumption will never be accurate. This is especially severe, as the estimation errors compound exponentially throughout the query plan [IC91]. This shows, that more accurate (but compact) statistics on data distributions (of base tables as well as intermediate results) are required to estimate intermediate results sizes.

The importance of statistics management has led to a plethora of approximation techniques, for which [GM99] have coined the general term "*data synopses*". Such techniques range from advanced forms of *histograms* (most notably, *V-optimal histograms* including multidimensional variants) [Poo97, GMP97, JKM<sup>+</sup>98, IP99] over *spline synopses* [KW99, KW00], *sampling* [CMN99, HNSS96, GM98], and *parametric curve-fitting techniques* [SLRD93, CR94] all the way to highly sophisticated methods based on *kernel estimators* [BKS99] or *Wavelets* and other transforms [MVW98, VW99, LKC99, CGRS00].

A logical cost model is a prerequisite for the following two cost components. In this work, we do not analyze logical cost models in more detail, but we assume that a logical cost model is available.

#### 2.1.1.2 Algorithmic Costs / Complexity

Logical costs only depend on the data and the query (i.e., the operators' semantics), but they do not consider the algorithms used to implement the operators' functionality. Algorithmic costs extend logical costs by taking the properties of the algorithms into account.

A first criterion is the algorithm's complexity in the classical sense of complexity theory. Most unary operator are in O(n), like selections, or  $O(n \log n)$ , like sorting; *n* being the input cardinality. With proper support by access structures like indices

or hash tables, the complexity of selection may drop to  $O(\log n)$  or O(1), respectively. Binary operators can be in O(n), like a union of sets that does not eliminate duplicates, or, more often, in  $O(n^2)$ , as for instance join operators.

More detailed algorithmic cost functions are used to estimate, e.g., the number of I/O operations or the amount of main memory required. Though these functions require some so-called "physical" information like I/O block sizes or memory pages sizes, we still consider them algorithmic costs and not physical cost, as these informations are system specific, but not hardware specific. The standard database literature provides a large variety of cost formulas for the most frequently used operators and their algorithms. Usually, these formulas calculate the costs in term of I/O operations as this still is the most common objective function for query optimization in database systems. We refer the interested reader, e.g., to [KS91, EN94, AHV95, GMUW02].

#### 2.1.1.3 Physical Costs / Execution Time

Logical and algorithmic costs alone are not sufficient to do query optimization. For example, consider two algorithms for the same operation, where the first algorithm requires slightly more I/O operations than the second, while the second requires significantly more CPU operations than the first one. Looking only at algorithmic costs, both algorithms are not comparable. Even assuming that I/O operations are more expensive than CPU operations cannot in general answer the question which algorithm is faster. The actual execution time of both algorithms depends on the speed of the underlying hardware. The physical cost model combines the algorithmic cost model with an abstract hardware description to derive the different cost factors in terms of time, and hence the total execution time. A hardware description usually consists of information such as CPU speed, I/O latency, I/O bandwidth, and network bandwidth. The next section discusses physical cost factors on more detail.

### 2.1.2 Cost Factors

In principle, physical costs are considered to occur in two flavors, *temporal* and *spatial*. Temporal costs cover all cost factors that can easily be related to execution time, e.g., by multiplying the number of certain events with there respective cost in terms of some time unit. Spatial costs contain resource consumptions that cannot directly (or not at all) be related to time. In the following, we briefly describe the most prominent cost factors of both categories.

#### 2.1.2.1 Temporal Cost Factors

As indicated above, physical costs are highly related to hardware. Hence, it is only natural that we distinguish different temporal cost factors according to the respective hardware components involved.

**Disk-I/O** This is the cost of searching for, reading, and writing data blocks that reside on secondary storage, mainly on disk. In addition to accessing the database

files themselves, temporary intermediate files that are too large to fit in main memory buffers and hence are stored on disk also need to be accessed. The cost of searching for records in a database file or a temporary file depends on the type of access structures on that file, such as ordering, hashing, and primary or secondary indexes. I/O costs are either simply measured in terms of the number of block-I/O operations, or in terms of the time required to perform these operations. In the latter case, the number of block-I/O operations is multiplied by the time it takes to perform a single block-I/O operation. The time to perform a single block-I/O operation is made up by an initial seek time (*I/O latency*) and the time to actually transfer the data block (i.e., block size divided by *I/O bandwidth*). Factors such as whether the file blocks are allocated contiguously on the same disk cylinder or scattered across the disk affect the access cost. In the first case (also called *sequential I/O*), I/O latency has to be counted only for the first of a sequence of subsequent I/O operations. In the second case (*random I/O*), seek time has to be counted for each I/O operation, as the disk heads have to be repositioned each time.

**Main-Memory Access** These are the costs for reading data from or writing data to main memory. Such data may be intermediate results or any other temporary data produced/used while performing database operations.

Traditionally, memory access costs were ignored in database systems. The reason for this was, that they were completely overshadowed by the dominating I/O costs in disk-base systems. As opposed to I/O costs, memory access cost were considered uniform, i.e., independent of both the physical locality and the physical order of accesses. This assumption was mainly true on the hardware in the 80's. Hence, main-memory DBMSs considered memory access costs to be included in the CPU costs.

In this thesis, we demonstrate that due to recent hardware trends, memory access costs have become a highly significant cost factor. Furthermore, we show that memory access on modern hierarchical memory systems depicts similar cost-related characteristics as I/O, i.e., we need to consider both latency and bandwidth, and we need to distinguish between sequential and random access patterns.

**Network Communication** In centralized DBMSs, communication costs cover the costs of shipping the query from the client to the server and the query's result back to the client. In distributed, federated, and parallel DBMSs, communication costs additionally contain all costs for shipping (sub-)queries and/or (intermediate) results between the different hosts that are involved in evaluating the query.

Also with communication costs, we have a latency component, i.e., a delay to initiate a network connection and package transfer, and a bandwidth component, i.e., the amount of data that can be transfer through the network infrastructure per time.

**CPU Processing** This is the cost of performing operations such as computations on attribute values, evaluating predicates, searching and sorting tuples, and merging tuples for join. CPU costs are measured in either CPU cycles or time. When using CPU cycles, the time may be calculated by simply dividing the number of cycles by

the CPU's clock speed. While allowing limited portability between CPUs of the same kind, but with different clock speeds, portability to different types of CPUs is usually not given. The reason is, that the same basic operations like adding two integers might require different amounts of CPU cycles on different types of CPUs.

Traditionally, CPU costs also cover the costs for accessing the respective data stored in main memory. However, we treat memory access costs separately.

Summarizing, we see that temporal cost are either caused by data access and/or data transfer (I/O, memory access, communication), or by data processing (CPU work).

#### 2.1.2.2 Spatial Cost Factors

Usually, there is only one spatial cost factor considered in database literature: *memory size*. This cost it the amount of main memory required to store intermediate results or any other temporary data produced/used while performing database operations.

Next to not (directly) being related to execution time, there is another difference between temporal and spatial costs that stems from the way they share the respective resources. A simple example shall demonstrate the differences. Consider to operations or processes each of which consumes 50% of the available resources (i.e., CPU power, I/O-, memory-, and network bandwidth). Further, assume that when run one at a time, both tasks have equal execution time. Running both tasks concurrently on the same system (ideally) results in the same execution time, now consuming all the available resources. In case each individual process consumes 100% of the available resources, the concurrent execution time will be twice the individual execution time. In other words, if the combined resource consumption of concurrent tasks exceed 100%, the execution time extends to accomodate the excess resource requirements. With spatial cost factors, however, such "stretching" is not possible. In case two tasks together would require more than 100% of the available memory, they simply cannot be executed at the same time, but only after another.

## 2.1.3 Types of (Cost) Models

According to their degree of abstraction, (cost) models can be classified into two classes: *analytical models* and *simulation models*.

**Analytical Models** In some cases, the assumptions made about the real system can be translated into mathematical descriptions of the system under study. Hence, the result is a set of mathematical formulas. We call this an analytical model. The advantage of an analytical model is that evaluation is rather easy and hence fast. However, analytical models are usually not very detailed (and hence not very accurate). In order to translate them into a mathematical description, the assumptions made have to be rather general, yielding a rather high degree of abstraction.

**Simulation Models** Simulation models provide a very detailed and hence rather accurate description of the system. They describe the system in terms of (a) simulation experiment(s) (e.g., using event simulation). The high degree of accuracy is charged at the expense of evaluation performance. It usually takes relatively long to evaluate a simulation base model, i.e., to actually perform the simulation experiment(s). It is not uncommon, that the simulation actually takes longer than the execution in the real system would take.

Simulation models are usually used in scenarios where a very detailed analysis as close as possible to the real system is required, but the actual system in not (yet) available. The most prominent example is processor development. The design of new CPUs is evaluated via exhaustive simulation experiments, first, to ensure the correctness and analyze the (expected) performance. The reason is, that producing functional prototypes in an early stage of the development process would be to expensive.

In database query optimization, though it would appreciate the accuracy, simulation models are not feasible, as the evaluation effort is far to high. Query optimization requires that costs of numerous alternatives are evaluated and compared as fast as possible. Hence, only analytical cost models are applicable in this scenario.

#### 2.1.4 Architecture and Evaluation of Database Cost Models

The architecture and evaluation mechanism of database cost models is tightly coupled to the structure of query execution plans. Due to the strong encapsulation offered by relational algebra operators, the cost of each operator, respectively each algorithm, can be described individually. For this purpose, each algorithm is assigned a set of *cost functions* that calculate the three cost components as described above. Obviously, the physical cost functions depend on the algorithmic cost functions, which in turn depend on the logical cost functions. Algebraic cost functions use the data volume estimations of the logical cost functions as input parameters. Physical cost functions are usually specializations of algorithmic cost functions that are parameterized by the hardware characteristics.

The cost model also defines how the single operator costs within a query have to be combined to calculate the total costs of the query. In traditional sequential DBMSs, the single operators are assumed to have no performance side-effects on each other. Thus, the cost of a QEP is the cumulative cost of the operators in the QEP [SAC<sup>+</sup>79]. Since every operator in the QEP is the root of a sub-plan, its cost includes the cost of its input operators. Hence, the cost of a QEP is the cost of the topmost operator in the QEP. Likewise, the cardinality of an operator is derived from the cardinalities of its inputs, and the cardinality of the topmost operator represents the cardinality of the query result.

In non-sequential (e.g., distributed or parallel) DBMSs, this subject is much more complicated, as more issues such as scheduling, concurrency, resource contention, and data dependencies have to considered. For instance, in such environments, more than one operator may be executed at a time, either on disjoint (hardware) resources, or (partly) sharing resources. In the first case, the total cost (in terms of time) is calculated as the maximum of the costs (execution times) of all operators running concurrently. In the second case, the operators compete for the same resources, and hence mutually influence their performance and costs. More sophisticated cost function and cost models are required here to adequately model this resource contention [LTS90, LST91, SE93, SYT93, LVZ93, ZZBS93, SHV96, SF96, GHK92].

## 2.2 Logical Cost Models / Estimation

Most DBMSs make certain assumptions on the underlying data in order to perform inexpensive estimations. Christodoulakis studied the implications of various common assumptions on the performance of databases [Chr83, Chr84]. The main set of assumptions studied by him are:

- **Uniformity of attribute values:** All possible values of an attribute have the same frequency in the data distribution.

- Attribute Independence: The data distributions of all attributes in a relation are independent of each other.

- Uniformity of queries: Queries refer attribute values with equal frequencies.

- **Constant number of records per block:** Each block of the file contains the same number of tuples.

- **Random placement:** Each record of the file has the same probability to qualify in a query, regardless of its placement among the pages of secondary storage.

He also showed that the expected cost of a query estimated using these assumptions is an upper bound on the actual expected cost. He demonstrated that existing systems using these assumptions tend to utilize expensive query evaluation strategies and that non-uniformity, non-independence, and non-random placement could be exploited in database design in order to reduce the system cost. In addition to providing such extensive motivation for better estimation techniques, his work also pioneered in the usage of several mathematical techniques such as *Schur concavity* [MO79] in database performance evaluation.

The System-R optimizer, assumed that the underlying data is uniform and independent ([SAC<sup>+</sup>79]). As a result, only the number of tuples and the lowest and highest values in each attribute are stored in the system catalogs, and it is assumed that all possible values between the two extremes occur with the same probability. Hence, very few resources are required to compute, maintain, and use these statistics. In practice, though, these assumptions rarely hold because most data tends to be nonuniform and has dependencies. Hence, the resulting estimates are often inaccurate. This was formally verified in the context of query result size estimation by Ioannidis and Christodoulakis in [IC91]. In their work they proved that the worst case errors incurred by the uniformity assumption propagate exponentially as the number of joins in the query increases. As a result, except for very small queries, errors may become extremely high, resulting in inaccurate estimates for result sizes and hence for the execution costs.

Several techniques have been proposed in the literature to estimate query result sizes, most of them contained in the extensive survey by Mannino, Chu, and Sager [MCS88]. The broad classes of various estimation techniques are described in the following sections.

### 2.2.1 Sampling-based Techniques

These techniques compute their estimates by collecting and processing random samples of the data, typically at query optimization time. There has been considerable amount of work done in sampling-based techniques for result size estimation [Ant92, ASW87, CMN99, GGMS96, HNSS96, HS92, HS95, LNS90, SN92, OR86, LS95]. Since these techniques do not rely on any precomputed information about the data, they are not affected by database updates and do not incur storage overheads. Another advantage of these techniques is their probabilistic guarantees on the accuracy of the estimates. Some of the undesirable properties of the sampling-based techniques are: (1) they incur disk I/Os and CPU overheads during query optimization, and (2) the information gathered is not preserved across queries and hence these techniques may incur the costs repetitively. When a quantity needs to be estimated once and with high accuracy in the presence of updates, the sampling technique works very well (e.g., by a query profiler). To overcome point (2), techniques for incremental maintenance of random samples have been developed in recent works [GMP97, GM98].

Another weak point of sampling is that the relations which are to be sampled have to be available. In other words, sampling can only be applied to base table or completely calculated intermediate results. Propagating samples through the operators of a complex query is generally not possible, especially with joins. These problems have been analyzed in detail in [CMN99, AGPR99, GGMS96].

#### 2.2.2 Parametric Techniques

These techniques approximate the actual data distribution by a parameterized mathematical distribution, such as the uniform distribution [SAC<sup>+</sup>79], multivariate normal distributions or Zipf distributions [Chr83]. The parameters for these distributions are obtained from the actual data distributions, and the accuracy of this approximation depends heavily on the similarity between the actual and parameterized distributions. The main advantage of this approach is the small storage overhead involved and the insignificant run-time costs. On the other hand, real data often does not resemble any simple mathematical distribution and hence such estimations may cause inaccuracies in estimates. Also, since the parameters are precomputed, this approach may incur additional errors if the database is updated significantly. Variants of this approach are the *algebraic* techniques, where the actual data distribution is approximated by a polynomial function. The coefficients of this function are determined using regression techniques [SLRD93]. A promising algebraic technique was proposed calling for adaptively approximating the distribution by a six-degree polynomial, whose coefficients are varied dynamically based on query feedback [CR94]. Some of the problems associated with the algebraic techniques are the difficulties in choosing the degree of the polynomial function and uniformly handling result size estimates for operators other than simple selection predicates. On the other hand, the positive results obtained in the work of Wei Sun et al. [SLRD93] on algebraic techniques indicates their potential applicability.

### 2.2.3 Probabilistic Counting Techniques

These techniques have been applied in the contexts of estimating the number of unique values in the result of projecting a relation over a subset of attributes ([GG82, FM85, SDNR96]). The technique for estimating the number of distinct values in a multiset, proposed by Flajolet and Martin [FM85] makes an estimate during a single pass through the data and uses a small amount of fixed storage. Shukla et al. applied this technique in estimating the size of multidimensional projections (the cube operator) [SDNR96]. Their experiments have shown that these techniques can provide more reliable and accurate estimates than the sampling-based techniques [SDNR96]. The applicability of these techniques to other operators is still an open issue.

#### 2.2.4 Non-parametric (Histogram-based) Techniques

These techniques approximate the underlying data distribution using precomputed tabular information (histograms). They are probably the most common techniques used in practice (e.g., they are used in DB2, Informix, Ingres, Microsoft SQL-Server, Oracle, Sybase, Teradata). Since they are precomputed, they may incur errors in estimation if the database is updated and hence require regular re-computation.

Most of the work on histograms is in the context of single operations, primarily selections. Specifically, Piatetsky-Shapiro and Connell dealt with the effect of histograms on reducing the error for selection queries [PSC84]. They studied two classes of histograms: equi-width histograms and equi-depth (or equi-height) histogram [Koo80]. Their main result showed that equi-width histograms have a much higher worst-case and average errors for a variety of selection queries than equi-depth histograms. Muralikrishna and DeWitt [MD88] studied techniques for computing and using multi-dimensional equi-depth histograms. By building histograms on multiple attributes together, their techniques were able to capture dependencies between those attributes. Several other researchers have dealt with "variable-width"histograms for selection queries, where the buckets are chosen based on various criteria [Koo80, KK85, MK88]. Kooi's thesis [Koo80] contains extensive information on using histograms inside an optimizer for general queries and the concept of variable-width histograms. The survey by Mannino, Chu, and Sager [MCS88] contains various references to work in the area of statistics on choosing the appropriate number of buckets in a histogram for sufficient error reduction. That work deals primarily with selections as well. Histograms for single-join queries have been minimally studied and then again without emphasis on optimality [Chr83, Koo80, MK88]. Probably the earliest efforts at studying optimality of histograms for result size estimation of join operators are those of Ioannidis and Christodoulakis [IC93, Ioa93]. They introduce two new classes of histograms, *serial* and *end-biased* histograms, and show that certain types of these classes, so called *V-optimal*(F,F) histograms, are optimal for worst-case errors of tree equality-join and selection queries. Practicality issues in computing the optimal histograms were not addressed in their work.

Some of the limitations of earlier work on histograms are as follows. First, they were mostly restricted to estimating the result sizes of a few operators such as selections and equi-joins. Second, barring the study by Ioannidis and Christodoulakis, most of the earlier work on histograms has been empirical in nature with almost no effort to identify optimal histograms. Finally, the computation techniques for the new classes of histograms proposed by [Ioa93] were too expensive to be of use in practice. Also, being restricted to predicates on single attributes, most of the earlier work on histograms did not deal with the effects of correlation between attributes from the same relation. Some of the work that did consider multiple attributes together [Ioa93] assumes that multi-dimensional histograms can be built in practice, but do not fully explore the practicality issues involved.

The work by Ioannidis and Poosala [IP95] marks probably the first effort to find a compromise between optimality and practicality of histograms. The work is continued and extended in [PIHS96] and [JKM<sup>+</sup>98].

There is lots of on-going work on and around the use of histograms in database query evaluation. Some recent issues are new techniques how to construct and maintain histograms efficiently [GMP97, CMN98, MVW98, AC99], and the use of histograms for approximate query answering [PGI99].

## 2.3 I/O-based Cost Models

Physical cost functions belong to the core of proprietary code of a database vendor. Their design, accurate tuning, and alignment with all other database components requires high level of expertise and knowledge of both hardware and database components. Hence, the vendors keep their physical cost functions as precious secrets.

Early work on System-R [SAC<sup>+</sup>79] uses a cost function balancing both factors I/O and CPU using a constant weight, a factor difficult to determine in practice. Moreover, given the discrepancy in I/O and CPU cost granularity, i.e., microseconds versus milliseconds, the former has become the prime factor in choosing a query execution plan.

A subsequent study on System-R\* [ML86] identified that in addition to the physical and statistical properties of the input data streams and the computation of selectivity, modeling buffer utilization plays a key role in accurate estimation. This requires using different buffer pool hit ratios depending on the levels of indexes as well as adjusting buffer utilization by taking into account properties of join methods, e.g., a relatively pronounced locality of reference in an index scan for indexed nested loop join [GLSW93].

With I/O being the dominant cost factor, database research has developed various

techniques to reduce the number of I/O operations needed to answer a query. Two of the most prominent of these techniques are in-memory buffers to cache frequently access pages of the database relations and indices to access a fraction of a table, e.g., as requested by a selection predicate, without the need to scan the whole table. While significantly improving database performance, these techniques make cost estimation more complicated, and it becomes more difficult to predict the exact number of I/O operations that will be needed to answer a query. A number of research works has been devoted to analyzing and predicting the impact of indices, buffer pools, and various buffer replacement strategies on the number of I/O operations, e.g., [CD85, SS86, Sac87, ML89, CS89, DYC95].

Numerous further I/O-based cost models appear in a database literature. However, in most cases, the cost models themselves a not the (primary) subject. Rather, they are just presented as necessary tools for query optimization. Though sharing some commonalities, most physical cost models are specific for the respective DBMS, its architecture, algorithms, data structures, and the hardware platform it runs on.

## 2.4 Main-Memory Cost Models

Relatively little work has been done on modeling of the performance cost of mainmemory DBMSs (MM-DBMSs). Early work on the design of database machines provides hints on the interdependencies of algorithms and memory access [Ozk86, Su88, BF89], but this research track has long been abandoned. This can partly be attributed to a lack of need, as use of MM-DBMS techniques have since been restricted to areas like real-time database systems (e.g., telecom switching, financial trading) that required relatively simple queries; say a hash-lookup in a single table.

In recent database literature, mainly the work around two research prototypes, IBM's *office-by-example (OBE)* and HP's *Smallbase*, has dealt with the issue of query optimization and cost modeling in main-memory environments.

### 2.4.1 Office-By-Example (OBE)

Whang and Krishnamurthy [WK90] discuss query optimization techniques applied in IBM's research prototype office-by-example (OBE). OBE is a memory-resident domain relational calculus database system that extends the concepts of *query-byexample* (*QBE*). To enable cost-based query optimization, they present a complete cost model. Due to the assumption that the data being processed is resident in main memory, the traditional database cost factor, I/O access, becomes obsolete. Rather, CPU computation cost now becomes dominant. Modeling CPU costs, however, is very difficult as too many parameters, like the software design, the hardware architecture, and even programming styles, may affect the CPU computation costs. A detailed analysis of larger systems to count the CPU cycles is virtually impossible. The solution that Whang and Krishnamurthy propose is to use an approach using both experimental and analytical methods. First, they identify the system's *bottlenecks* using an execution analyzer / profiler. Only bottlenecks will be used to model the system's CPU cost. To prevent the cost model from drifting frequently due to changes in the program, the bottlenecks are improved as much as possible with reasonable effort. The next step is then to find, by experiments, *relative weights* of different bottlenecks and to determine their *unit costs*. Finally, they develop comprehensive cost formulas based on these unit costs.

For OBE, Whang and Krishnamurthy identified the following bottlenecks and measured the respective unit costs:

- 1. evaluating the expressions involved in predicates (unit  $cost = C_1$ );

- 2. comparison operations needed to finally determine the outcome of predicates (unit  $cost = C_4$ );

- 3. retrieving a tuple from a (memory-resident) relation (unit cost =  $C_3$ );

- 4. unit operation in creating an index (creating an index on a relation of *n* tuples takes  $n \log_2 n$  such unit operations; unit cost =  $C_4$ );

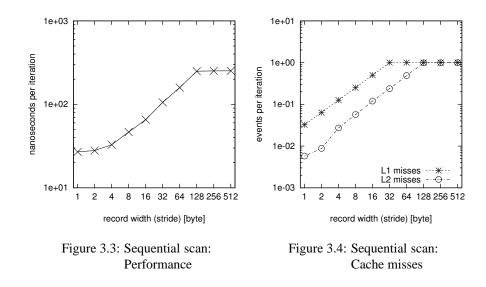

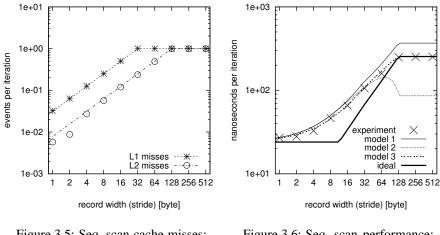

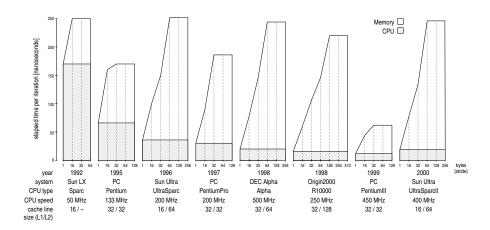

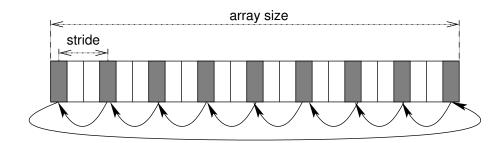

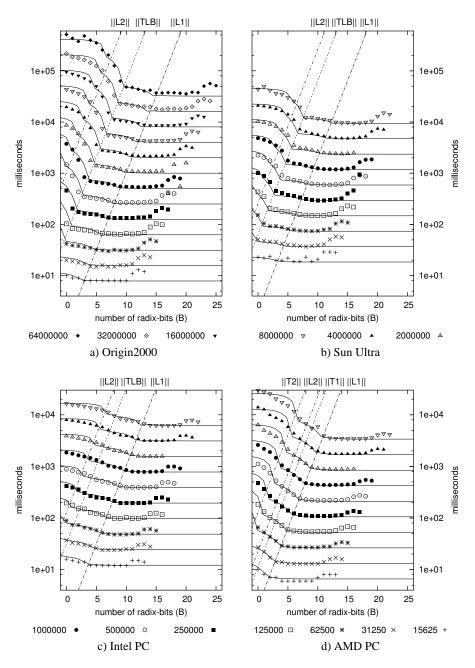

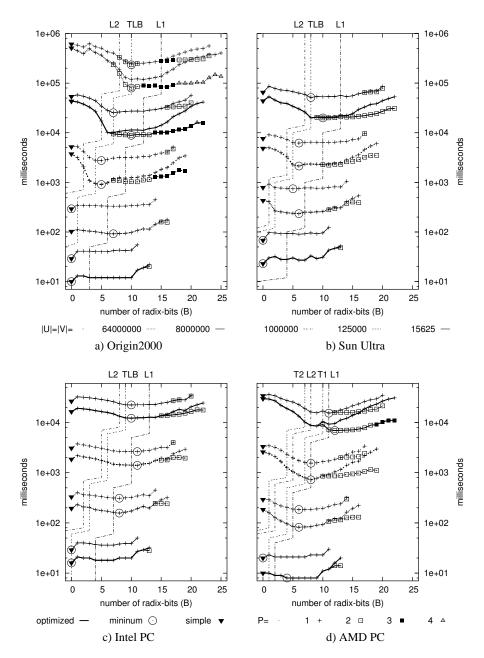

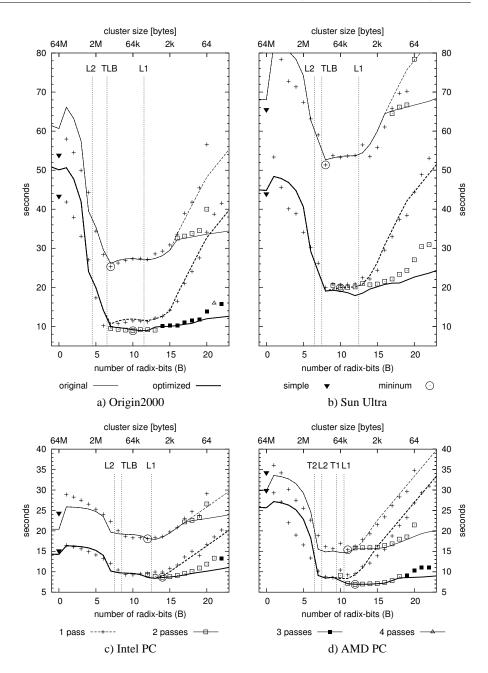

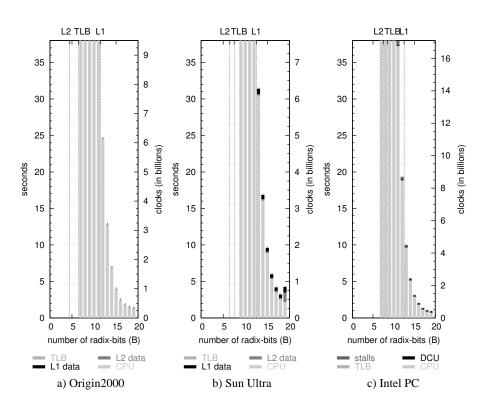

- 5. unit operation in the sorting needed to prepare a multi-column index (unit cost  $= C_5$ ).